3-37

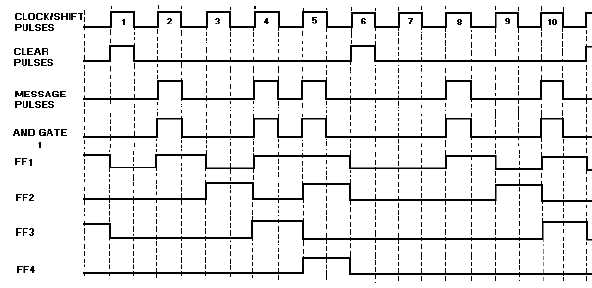

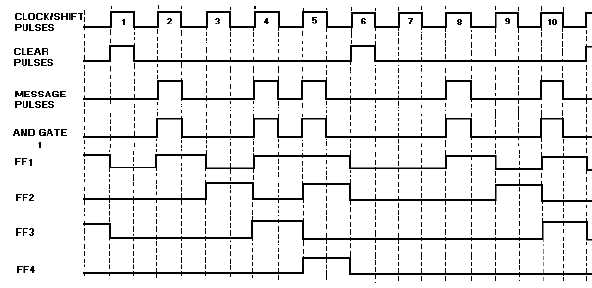

Figure 3-33. —Serial-to-parallel conversion timing diagram.

A CLEAR pulse resets all the FFs at CP1. At CP2, the most significant bit of the data is input to

AND gate 1. This HIGH along with the clock pulse causes AND gate 1 to output a HIGH. The HIGH

from the AND gate and the clock pulse applied to FF1 cause the FF to set. FFs 2, 3, and 4 are held reset.

At this point, the MSD of the data has been shifted into the register.

The next bit of data is a 0. The output of AND gate 1 is LOW. Because of the inverter on the K input

of FF1, the FF senses a HIGH at that input and resets. At the same time this is occurring, the HIGH on the

J input of FF2 (from FF1) and the CLK cause FF2 to set. The two MSDs, 1 and 0, are now in the register.

CP4 causes FF3 to set and FF2 to reset. FF1 is set by the CLK pulse and the third bit of the number.

The register now contains 01012, as a result of shifting the first three bits of data.

The remaining bit is shifted into the register by CP5. FF1 remains set, FF2 sets, FF3 resets, and FF4

sets. At this point, the serial transfer is complete. The binary word can be sampled on the parallel output

lines. Once the parallel data is transferred, a CLEAR pulse resets the FFs (CP6), and the register is ready

to input the next word.

Scaling Operation

Using the shift register shown in figure 3-31 for scaling a number is quite simple. The number to be

scaled is loaded into the register either in serial or parallel form. Once the data is in the register, the

scaling takes place in the same manner as that for shifting the data for serial output. A single clock pulse

will cause each bit of data to shift one place to the left. Remember that each shift is the equivalent of

increasing the value by a power of 2. The scaled data is read from the parallel outputs. Care must be taken

not to over shift the data to the point that the MSDs are shifted out of the register.

Q54. Serial-to-parallel and parallel-to-serial conversions are accomplished by what type of circuit?

Q55. What type of data transfer requires the most time?

Q56. What is the main disadvantage of parallel transfer?

Q57. How many FFs would be required for an 8-bit shift register?