33

4-32. Which of the following statements is

correct concerning D flip-flops?

1. The output is delayed up to one

clock pulse

2. Input data is delayed until it

coincides with the clock

3. The clock is delayed until it

coincides with the input data

4. The output is always a square wave

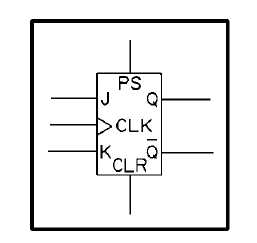

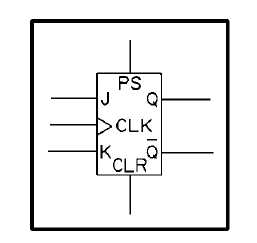

Figure 4F.—Standard symbol for a J-K flip-flop.

WHEN ANSWERING QUESTIONS 4-33

THROUGH 4-36, REFER TO FIGURE 4F.

4-33. The flip-flop shown in the figure may be

used in place of which of following flip-

flops?

1. R-S

2. T

3. D

4. Each of the above

4-34. With the clock applied and J and K

inputs held HIGH, what is the output at

Q?

1. Constant HIGH

2. Constant LOW

3. Toggle at one half the clock

frequency

4. Toggle at twice the clock frequency

4-35. What will be the Q output if K is HIGH

and CLK goes HIGH?

1. HIGH

2. LOW

4-36. A pulse on which of the following

inputs will cause the flip-flop to set

regardless of the other inputs?

1. CLK

2. CLR

3. J or K

4. PR or PS

4-37. The circuit which generates a timing

signal to control operations is called

a/an

1. clock

2. counter

3. oscillator

4. bistable multivibrator

4-38. Which of the following statements is

true regarding astable multivibrators

used as clocks?

1. As multivibrator frequency

increases, stability decreases

2. Output 2 will have a higher voltage

than output 1

3. The frequency stability may be

increased by applying a higher

frequency trigger

4. A trigger of lower frequency will

stabilize the output frequency

4-39. Which of the following types of circuits

will produce a stable clock when

triggered by an outside source?

1. R-S flip-flop

2. Bistable multivibrator

3. One-shot multivibrator

4. D flip-flop